ARM64: Armv9.2 Дизасемблер

Суцільний TL;DR

Побудова дизасемблера зазвичай підпорядковується наступному сценарію: спочатку ми ретельно екстрагуємо з офіційної документації на архітектуру опкодів з ISA PDF та розкладаємо біти по групах, які допоможуть нам в подальшому вручну групувати інструкції. Загальний формат інструкції наступний:

+---------------------= 32/64-bit

|

| 0 0 0 0 --------= SME

| 0 0 1 0 --------= SVE

| 1 0 0 x --------= Data Processing Immediate

| 1 0 1 x --------= Branching, System, Exceptions

| x 1 x 0 --------= Loads and Stores

| x 1 0 1 --------= Data Processing Register

| 1 1 1 1 --------= NEON Scalar

| 0 1 1 1 --------= NEON Vector

| | | | |

| | | | |

7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0 7 6 5 4 3 2 1 0

+-------------+ +-------------+ +-------------+ +-------------+

| MSB | | | | | | LSB |

+-------------+ +-------------+ +-------------+ +-------------+

Післія документування алфавітного показчика 6.A64.LST ми групуємо інструкції по групах, та візуально визначаємо кількість типів інструкції, яких добре аби було найменше, в нашому випадку 16, тобто на тип по 4 біти, і якшо робити діспатч по першому байту то для таблиці першого діспатча потрібно 128 байт. У файлі 6.A64.GROUPS показані типи інструкцій:

| 31-21 | 20-16: Rm | F | 14-10: Ra | 9-5: Rn | 4-0: Rd | Description

+-----------------------+-----------+---+-----------+-----------+-----------+--------------------------

| s q x t t t t z a r w | x x x x x | x | x x x x x | x x x x x | x x x x x | % 0-way PURE:

| s q x t t t t z a r w | x x o o o | x | x x x x x | x x o o o | Rd | % 1-way REG:

| s q x t t t t z a r w | Rm | c | c c c x x | Rn | x n z c v | % 2-way REG RIGHT:

| s q x t t t t z a r w | x x x x x | x | x Z x x M | Rn | Rd | % 2-way REG LEFT:

| s q x t t t t z a r w | Rm | x | x x x x x | Rn | Rd | % 3-way REG:

| s q x t t t t z a r w | Rm | x | Ra | Rn | Rd | % 4-way REG:

| s q x t t t | imm26 | % 0-way BRA:

| s q x t t t t z a r w | imm5 | c | c c c x x | Rn | x n z c v | % 1-way REG IMM:

| s q x t t t t z a r w | imm16 | Rd | % 1-way REG BIG IMM:

| s q x t t t t z | imm19 | Rd | % 1-way REG LARGE IMM:

| s q x t t t t z a r w | imm9 | x x | Rn | Rd | % 2-way REG IMM:

| s q x t t t t z a r | imm12 | Rn | Rd | % 2-way REG BIG IMM:

| s q x t t t t z a r | immr | imms | Rn | Rd | % 2-way REG PAIR IMM:

| s q x t t t t z a r w | Rm | imm6 | Rn | Rd | % 3-way REG RIGHT IMM:

| s q x t t t t z a r | imm7 | Ra | Rn | Rd | % 3-way REG LEFT IMM:

| 31-21 | 20-16: Rm | F | 14-10: Ra | 9-5: Rn | 4-0: Rd | Description

+-----------------------+-----------+---+-----------+-----------+-----------+-------------------

| s q x t t t t z a r w | Rm | x | x x x x x | Rn | Rd | % 3-way REG:

| s q x t t t t z a r w | a b c d e | x | x x x x x | f g h i j | Rd | % 1-way REG:

| s q x t t t t z a r w | imm5 | x | x x x x x | Rn | Rd | % 2-way REG IMM:

| s a x t t t t z a r w | Rm | 0 | Ra | Rn | Rd | % 4-way REG:

| s q x t t t t z a r w | Rm | 0 | imm4 | 0 | Rn | Rd | % 3-way REG IMM:

| 31-21 | 20-16: Rm | F | 14-10: Ra | 9-5: Rn | 4-0: Rd | Description

+-----------------------+-----------+---+-----------+-----------+-----------+-------------------

| s q x t t t t z a r w | Zm | x | x x x x x | Zn | Zd | % 3-Way REG:

| s q x t t t t z a r w | x x x x x | x | x x | imm8 | Zd | % 1-Way REG IMM:

| 31-21 | 20-16: Rm | F | 14-10: Ra | 9-5: Rn | 4-0: Rd | Description

+-----------------------+-----------+---+-----------+-----------+-----------+-------------------

| s q x t t t t z a r w | x x x x x | x | y y z z z | a b c d e | f g h i j | % 0-Way PURE:

| s q x t t t t z a r w | x x x x x | x | y y z z z | Zn | a b c d e | % 1-Way REG LEFT:

| s q x t t t t z a r w | x x x x x | x | y y z z z | a b c d e | Zd | % 1-Way REG RIGHT:

| s q x t t t t z a r w | Zm | x | y y z z z | Zn | a b c d e | % 2-Way REG:

| s q x t t t t z a r w | Rn | x | y y z z | imm6 | Rd | % 2-Way REG IMM:

Всього ARM64 має 4 головних розширення (по главам):

6) Скалярне ядро A64;

7) FPU/SIMD ядро яке називається NEON;

8) Векторне SVE ядро з 2048-бітними регістрами;

9) Матричне ядро SME.

A64: R0-R30 -- general purpose registers (63..0: Xn, 31..0: Wn)

R31 -- zero register (63..0)

SP -- stack pointer (63..0)

PC -- program counter (63..0)

NEON: V0-V31 -- FPU/SIMD registers (127..0: Qn, 63..0: Dn, 31..0: Sn, 15..0: Hn, 7..0: Bn)

FPCR,FPSR -- FPU/SIMD status registers (63..0)

SVE: P0-P15 -- SVE predicate registers (255..0, ..., 15..0)

FFR -- SVE first fault register (63..0)

Z0-Z31 -- SVE registers (2047..0, ..., 127..0: Qn)

(63..0: Dn, 31..0: Sn, 15..0: Hn, 7..0: Bn)

Інструкції цих розширень знаходяться у відповідних файлах:

6.A64.LST, 7.FPU.LST, 8.SVE.LST, 9.SME.LST.

31...28 27...24 23...20 19...16 15...12 11...08 07...05 04...00

+---------+---------+---------+---------+---------+---------+---------+---------+

| RAS | DIT | AMU | CSV2 | STATE3 | STATE2 | STATE1 | STATE0 | PFR #0

+---------+---------+---------+---------+---------+---------+---------+---------+

| GIC | VIRT | SEC | GenTimer| VIRT | MProgMod| SEC | ProgMod | PFR #1

+---------+---------+---------+---------+---------+---------+---------+---------+

| | RAS | SSBS | CSV3 | PFR #2

+---------+---------+---------+---------+---------+---------+---------+---------+

| Implementer | Variant | Arch | Primary Part Number | Revision| MIDR

+---------+---------+---------+---------+---------+---------+---------+---------+

| FPround | FPshVec | FPsqrt | FPdiv | FPtrap | FPDP | FPSP | SIMDreg | MVFR #0

+---------+---------+---------+---------+---------+---------+---------+---------+

| SIMDmac | FPHP | SIMDHP | SIMDHP | SIMDint | SIMDLS | FPDNaN | FPFtZ | MVFR #1

+---------+---------+---------+---------+---------+---------+---------+---------+

| | FPmisc | SIMDmisc| MVFR #2

+---------+---------+---------+---------+---------+---------+---------+---------+

| | Divide | Debug | Coproc | CmpBr | BitField| BitCount| Swap | ISAR #0

+---------+---------+---------+---------+---------+---------+---------+---------+

| Jazelle |Interwork|Immediate| IfThen | Extend | ExceptAR| Except | Endian | ISAR #1

+---------+---------+---------+---------+---------+---------+---------+---------+

| Reversal| PSR_AR | MultU | MultS | Mult | MAI | MemHint |LoadStore| ISAR #2

+---------+---------+---------+---------+---------+---------+---------+---------+

| T32EE | TrueNOP | T32Copy | TabBr | SynPrim | SVC | SIMD | Saturate| ISAR #3

+---------+---------+---------+---------+---------+---------+---------+---------+

| SWP | PSR_M | SynPrim | Barrier | SMC | WB | WS | Unpriv | ISAR #4

+---------+---------+---------+---------+---------+---------+---------+---------+

| VCMA | RDM | | CRC32 | SHA2 | SHA1 | AES | SEVL | ISAR #5

+---------+---------+---------+---------+---------+---------+---------+---------+

| | I8MM | BF16 | SPECRES | SB | FHM | DP | JSCVT | ISAR #6

+---------+---------+---------+---------+---------+---------+---------+---------+

| InnerShr| FCSE | AuxReg | TCM | ShareLvl| OuterShr| PMSA | VMSA | MMFR #0

+---------+---------+---------+---------+---------+---------+---------+---------+

| BPred | L1TstCln| L1Uni | L1Hvd | L1UniSW | L1HvdSW | L1UniVA | L1HvdVA | MMFR #1

+---------+---------+---------+---------+---------+---------+---------+---------+

| HWAccFlg| WFIStall| MemBarr | UniTLB | HvdTLB | L1HvdRng| L1HvdBG | L1HvdFG | MMFR #2

+---------+---------+---------+---------+---------+---------+---------+---------+

63...60 59...56 55...52 51...48 47...44 43...40 39...36 35...32 31...28 27...24 23...20 19...16 15...12 11...08 07...05 04...00

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

| CSV3 | CSV2 | RME | DIT | AMU | MPAM | SEL2 | SVE | RAS | GIC | AdvSIMD | FP | EL3 | EL2 | EL1 | EL0 | PFR #0

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

| | NMI | CSV2 | RNDRtrap| SME | | MPAM | RAS | MTE | SSBS | BT | PFR #1

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

| RNDR | TLB | TS | FHM | DP | SM4 | SM3 | SHA3 | RDM | TME | ATOMIC | CRC32 | SHA2 | SHA1 | AES | RES0 | ISAR #0

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

| LS64 | XS | I8MM | DGH | BF16 | SPECRES | SB | FRINTTS | GPI | GPA | LRCPC | FCMA | JCVT | API | APA | DPB | ISAR #1

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

| | RES0 | PAC | HBC | MOPS | APA3 | GPA3 | RPRES | WFxT | ISAR #2

+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+---------+

Регістри архітектури ARM64 розширюють регістри ARM32 і відповідають за визначення імплементації певних секцій інструкцій різної гранулярності. Деякі бітові секції відповідають за конкретні інструкції, а деякі за архітектурні розширення.

A32 ISAR #2 LoadStore:

0000 No additional load/store instructions implemented.

0001 Adds the LDRD and STRD instructions.

0010 Adds Load Acquire (LDAB, LDAH, LDA, LDAEXB, LDAEXH, LDAEX, LDAEXD) and

Adds Store Release (STLB, STLH, STL, STLEXB, STLEXH, STLEX, STLEXD) instructions.

A32 ISAR #0 Divide:

0000 None implemented.

0001 Adds SDIV and UDIV in the T32 instruction set.

0010 Adds SDIV and UDIV in the A32 instruction set.

Для визначення розширень на поточному процесорі використовується інструкція MSR. Передбачається, що редактор BE, який буде використовувати бібліотеку DASM-ARM, зможе визначати на ARM процесорах доступний набір розширень.

MSR #sysreg, Xt

MSR Xt, #sysreg

Інструкція доступу до відлагоджувальних та трасувальних системних регістрів.

o: {0,3,4} — відлагоджувальні системні регістри.

o: {1} — трасувальні системні регістри.

+----+-----------------------+-----------+---+-----------+-----------+-----------+

| No | 31-21 | 20-16: Rm | F | 14-10: Ra | 9-5: Rn | 4-0: Rd |

+----+-----------------------+-----------+---+-----------+-----------+-----------+

| | 1 1 0 1 0 1 0 1 0 0 L | 1 0 o o o | n | n n n m m | m m o o o | Rt |

+----+---------------------------------------------------------------------------+

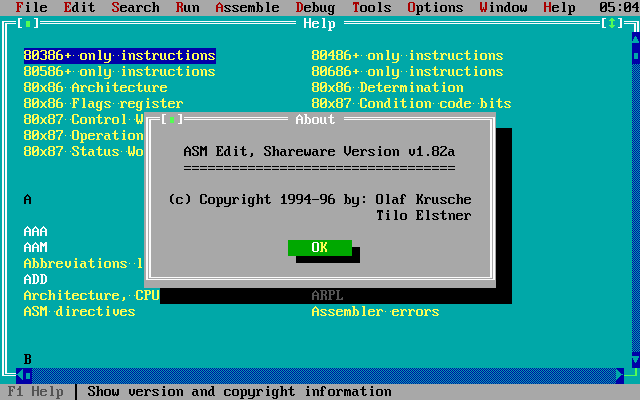

Також хочеться, аби BE, як і оригінальний AsmEdit мав подібний вбудований довідних по всім інструкціям, але тут вже йдеться про переклад великої книжки на 1600 інструкцій, цю роботу потрібно розділити між студентами.

Вступ

Ця вправа може стати лабораторною роботою, або курсовою роботою по курсу "КВ-123-17: Мікропроцесорні архітектури" для студентів першого курсу, які тільки знайомляться з існуючими архітектурами.

Огляд існуючих дизасемблерів

Код

Репозиторій проекту github.com/asmedit/dasm-arm.

Рекомендована література

[1]. ARM Architecture Reference Manual. 2022.